离子束刻蚀机厂家分享路技集成电路的发展

离子束刻蚀机厂家分享路技集成电路的发展:

1958年,美国德州仪器公司展示了全球第一块集成电路板,电线将5个电子元件连接在起,这标志着世界从此进入集成电路的时代,1959年,美国贝尔实验室的马丁・艾特拉Martin Atalla)和道旺・卡恩( Dawon Kahng)研发了首个绝缘栅场效应晶体管(FET)他们的成功要素是通过控制“表面态”的影响使得电场能渗入半导体材料。在研究热生长硅氧化层的过程中,他们发现在金属层(M)、氧化层(O绝缘)和硅层(S半导体)的结构中,这些“表面态”会在硅和其氧化物的交界处大大降低。这样,加在概上的电场能通过氧化层影响硅层,这就是MOS名称的由来。由于原始的MOS器件速度偏慢,且未能解决电话设备中所面临的问题,这项研究破停了下来。但仙童半导体( Fairchild)公司和美国无线电(RCA)公司的研究者们认识到了MOS器件的优点。在20世纪60年代,卡尔・寒宁格( Karl Nininger)和查尔斯・程勒( Charles Meuller)在美国无线电公司制造出了金属氧化物半导体晶体管。飞兆半导体公司的支唐(C.T.Sah)制造了一个带控制极的MOS四极管,随后,MOS晶体管开始用于集成电路器件开发

1962年,弗雷德・海曼( Fred Heiman)和史蒂文・夫斯坦( Steven Hofstein)在美国无线电公司制造了一个实验性的由16个品体管组成的单芯片集成电路器件リ,在1963年一篇作者为飞兆研发实验室萨支唐和弗兰克・万拉斯( Frank Wanlass)的论文中显示,当处于以互补性对称电路配置连接p沟道和n-沟道MOS品体管形成逻电路时(今日称为CMOS,即互补型场效应管),这个电路的功耗几乎接近为零。弗兰克・万拉斯将这一发明申请了CMOS技术为低功耗集成电路打下了基础并成为今日的主流数字集成电路的生产技术。

1963年,在定义开发标准逻辑电路中,晶体管-晶体管逻(TTL)集成电路因其速度、成本和密集度优势而确立成为20世纪六七十年代流行的标准逻构造模块。1964年,混合微型电路达产量高峰,IBM系统/360计算机系列发展的多芯片SLT封装技术进入大批量生产。同年,第一块商用MOS集成电路诞生,通用微电子公司用金属氧化物半导体工艺取得了比双极型集成电路高的集成度,并且用这项技术制造了第一个计算器芯片组。1968年,费德里克·法格( Federico Faggin)和汤姆・克菜恩( Tom Klein)利用硅栅结构(取代了金属栅)改进了MOS集成电路的可靠性、速度和封装集成度。法格设计了第一个商用硅栅集成电路(飞兆3708)。1971年,为了减少运算器设计需要的芯片数,英特尔公司的工程师创造了第个单片微处理器(CPU)i4004。1974年,用于液晶显示数字手表的集成电路是第一块集成整个电子系统到单个硅片上的产品(SoC)。1978年,用户可编程逻器件(可程序化行列逻)诞生。单片存储器公司的约・比克纳( John Birkner)和H.T.Chua为了能让客户快速定义逻辑功能,他们研发了易用的可编程行列逻辑(PAL.)器件和软件工具1979年,单片数字信号处理器诞生。贝尔实验室的单片DSP-1数字信号处理器器件结构使电子开关系统

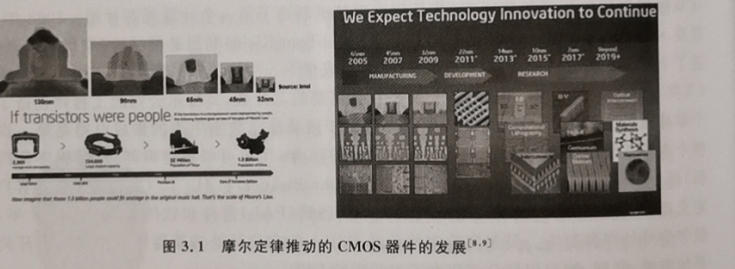

更加完善,同期,德州仪器公司研发了可编程的DSP1965年仙童半导体公司研发总监戈登・摩尔( Gordon Moore)曾写过一份内部文件,他整理了1959-1964年开发的5组产品并以芯片的集成度和单个器件的低成本做成图表,然后划条连线穿过这些点。从这个图上戈登・摩尔发现每个新芯片大体上包含其前任两倍的容量,而且每个新芯片的产生都是在前一个芯片产生后的18-24个月内。如果按这个趋势继续计算能力相对于时间周期将呈指数式的上升。摩尔的观察结果,就是现在所谓的摩尔定律。他当时预测,在今后的10年中芯片上的器件数将每年翻一番,并会在1975年达到6500个“对集成电路而言,降低成本具有相当的吸引力。随着技术的发展使其能在单芯片上集成愈来愈多的电路功能,成本的优势会继续增长。1975年,已加入英特尔公司的戈登・尔对他自己提出的摩尔定律”做了一次修改,并指出芯片上集成的晶体管数量将每两年翻一番先进的集成电路是微处理器或多核处理器的“核心( cores)”,可以控制从计算机到手机等数字产品的一切。存储器和ASIC是其他集成电路家族的例子,对于现代信息社会非常重要。虽然设计开发一个复杂集成电路的成本非常高,但是当分散到通常以百万计的产品上,每个IC的成本将会显著降低。1C的性能很高,因为小尺寸带来短路径,使得低功率逻辑电路可以在快速开关速度下应用。近些年,随着1C持续向更小的外形尺寸发展,每个芯片可以封装史多的电路。这样既增加了单位面积容量,又可以降低成本和增加功能。总之,随着外形尺す缩小,几乎所有的指标都改善了,单位成本和开关功耗下降,速度得到提升。但是,伴随着尺寸缩小,器件的漏电流( leakage current)也会随之增大,因此,对于终用户的速度和功率消耗增加非常明显,制造商需要使用更好的图形设计及工艺优化来应对这样严峻的挑战。这个过程和在未来几年所期望的进步,在半导体国际技术路线图( nternational TechnologyRoadmap for Semiconductors,ITRS)中有很好的描述。图3.1描述了英特尔系列处理器近15年在半导体制造工艺上的演变,从130nm硅栅到65mm硅栅制造技术,再到32nm金属栅制造工艺,目前新的鳍式场效应管金属栅处理器,达到半导体制造的巅峰。与传统平面晶体管比,鳍式场效应晶体管( FINFET)由于采用了立体的三维结构,大大增加了栅级的控制面积,因此可以大幅缩短晶体管闸长和减少漏电流,降低尺す微缩带来的短沟道效应。英特尔公司2011年用22nm节点工艺推出了商业化的 FINFET:2014年底,三星公司实现了14 nm FINFET工艺量产,为未来的移动通信设备提供更快、更省电的处理器。紧随其后,台积电公司2015年推出增强型16 nm FINFET+。目前苹果公司的高端手机 iphone7和 iphone7plus的处理器即分别采用了业界主流的 FINFEI技术,中国海思公司研发的麒麟950等高端移动芯片也采用了 FINFET工艺。在逻辑电路工艺中,前段逻辑蚀刻着重在于场效应管的搭建,而后段蚀刻聚焦于电路连线。

下一条: 离子束刻蚀机厂家分享中性粒子束刻蚀技术